#### DATA SHEET

# W5643A DDR5 78-ball BGA Interposer

## **Overview**

The W5643A DDR5 x4/x8 78-ball BGA interposer enables probing of embedded memory DRAM from the ball grid array with Keysight Technologies, Inc. U4164A logic analyzers. The Keysight W5643A DDR5 78-ball BGA interposers for logic analyzers enable viewing of traffic on industry standard DDR5 78-ball DRAMs with the Keysight U4164A logic analysis systems.

The W5643A DDR5 BGA interposers are designed to take full advantage of quad sample state mode on U4164A modules with Option 02G, requiring only a single probe point for up to four samples at two different thresholds. First in the industry, the W5643A DDR5 BGA interposers are thinner than any previous BGA interposers with a small KOV (keep out volume).

W5643A Series BGA interposers are designed to capture DDR5 protocol (CA/CS#/ CK) for data rates up to 5Gb/s and capture DDR5 DQ at data rates up to 4Gb/s.<sup>1</sup>

#

#### **Key Benefits**

- Probes a 78-ball DDR5 single channel x4 or x8 DRAM chip

- Access signals with one each U4208A and U4209A cables

- Measurement timing skews within +/- 25 psec

- Interposers are delivered with RC (resistor/ capacitor) networks

1 Maximum transfer rates are subject to variables in the signal integrity of the system under test and specifications of the U4164A logic analyzer module. U4164A specifications: minimum eye size of 100mV x 100ps at the RC network on the W5643A, maximum CK frequency of 2.5GHz, and maximum data rate of 4GT/s.

# The DDR5 BGA Interposer Advantage

| Features                                                                                                                                                                   | Benefits                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connects directly to the DDR5 BGA balls.                                                                                                                                   | Eliminates reflections from mid-bus probing<br>methods. Also eliminates design time,<br>prototype builds, and trace routing required<br>to design in alternative probing methods. |

| <ul> <li>Supports/Enables:</li> <li>DDR5 78 ball single die, stacked, or quad x4, x8 DRAM at data rates up to 5Gb/s for protocol analysis and 4Gb/s DQ capture.</li> </ul> | Get complete signal access to the DDR5 signals critical to your debug.                                                                                                            |

| <ul> <li>DDR eyescan display of DDR5 signals<br/>into logic analyzer module from BGA<br/>interposer</li> </ul>                                                             |                                                                                                                                                                                   |

| <ul> <li>DDR5, decode, functional compliance<br/>and performance analysis using<br/>optional licensed software</li> </ul>                                                  |                                                                                                                                                                                   |

| • Using APS (Advanced Probe Settings <sup>2</sup> )                                                                                                                        |                                                                                                                                                                                   |

| Supports either leaded or lead-free solder.                                                                                                                                | Easily works with all solder finishes.<br>Designed to tolerate lead-free soldering<br>temperature profiles.                                                                       |

| Contract manufactures available for<br>those without the in-house expertise or<br>facilities for soldering BGAs.                                                           | Eliminates the need to develop BGA soldering expertise.                                                                                                                           |

| Flexible "wings" with ZIF connectors.                                                                                                                                      | Ensures reliable connection to the ZIF probes.                                                                                                                                    |

|                                                                                                                                                                            | Enables placement of the probe cables around adjacent components.                                                                                                                 |

|                                                                                                                                                                            | Minimizes the torque to the balls of the BGA.                                                                                                                                     |

2 To enable Advanced Probe Settings refer to Technical Overview 5991-0799EN.

10000022

# **Technical Characteristics**

Keysight Technologies W5643A BGA Interposers enable probing of embedded DDR5 DRAM (x4 and x8) directly at the ball grid array using Keysight U4164A Logic Analyzers with option U4164A-02G.

Ball Count: 78Package Size: maximum 11mm x 14mm<sup>3</sup>Connectors: 2 Zero-Insertion Force (ZIF) Connectors

### Key performance features:

- Probes a 78-ball DDR5 single channel x4 or x8 DRAM chip, JEDEC MO-207M footprint variation DT-z, with a maximum DRAM package size of 11mm x14mm

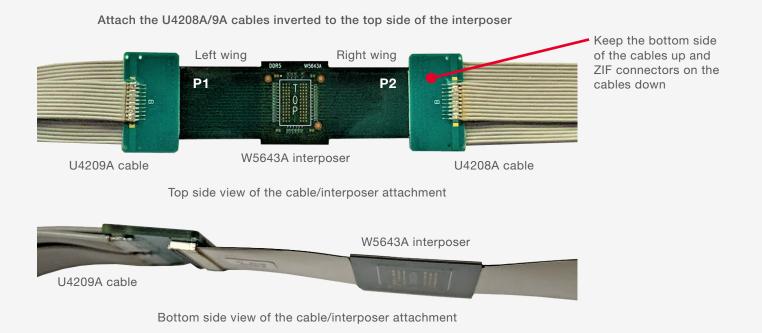

- Access signals with one each U4208A and U4209A cables with Zero-insertion force (ZIF) connectors. (sold separately).

- Measurement timing skews within +/- 25 psec achieved by matched trace lengths from DDR5 balls to test point

- Interposers are delivered with RC (resistor/capacitor) networks for logic analyzer probing installed on top of each DDR5 BGA interposer.

- W5643A ships with a riser to provide clearance for surrounding devices

### W5643A includes:

- DDR5 x4/x8 78-ball BGA interposer

- DDR5 x4/x8 78-ball BGA riser

### W5643A requires:

- Qty (1) U4208A Probe/cable, 61-pin ZIF, no RC, 160-pin direct connect to LA

- Qty (1) U4209A Probe/cable, 61-pin ZIF, no RC, 160-pin direct connect to LA

- Qty (1) U4164A logic analyzer module with option -02G speed grade option, chassis and either an embedded controller or host PC

- Qty (1) B4661A memory Analysis SW, no additional charge for base SW with default configurations and State mode tuning assistance.

### Recommended for use with W5643A:

• Qty (1) B4661A-5FP/-5TP/-5NP DDR5 Analysis and Compliance SW licensed option for rapid navigation, debug, and validation of DDR5 system protocol.

<sup>3</sup> maximum of 11mm x 14mm DDR5 DRAM package can fit on top of DDR5 x4/x8 BGA interposer without an additional riser or socket (not provided) to provide clearance for the RC components.

# **Dimensional Drawings**

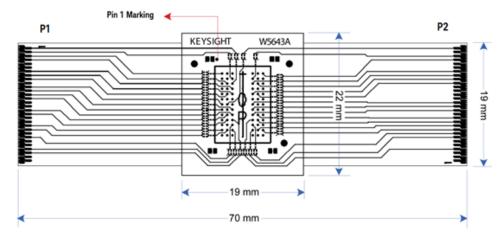

W5643A dimensions – Top view

0.5 mm thick in the BGA field, (not including BGA balls).

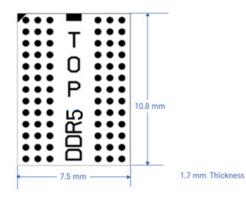

W5643A riser dimensions - Top view

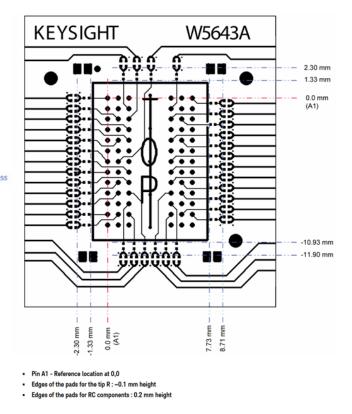

Dimensions of 78-ball footprint on W5643A

#### Note: All measurements in millimeters

|   | 1       | 2    | 3     | 4         | 5        | 6         | 7      | 8    | 9       |   |

|---|---------|------|-------|-----------|----------|-----------|--------|------|---------|---|

| Α | LBDQ    | GND  | VPP   | $\bowtie$ | $\succ$  | $\succ$   | ZQ     | GND  | LBDQS   | A |

| в | VDD     | VDDQ | DQ2   | $\bowtie$ | $\times$ | $\bowtie$ | DQ3    | VDDQ | VDD     | В |

| С | GND     | DQ0  | DQS_t | $\bowtie$ | $\times$ | ${\succ}$ | DM_n   | DQ1  | GND     | С |

| D | VDDQ    | GND  | DQS_c | $\succ$   | $\times$ | $\succ$   | TDQS_c | GND  | VDDQ    | D |

| E | VDD     | DQ4  | DQ6   | $\succ$   | $\times$ | $\succ$   | DQ7    | DQ5  | VDD     | E |

| F | GND     | VDDQ | GND   | $\times$  | Х        | $\succ$   | GND    | VDDQ | GND     | F |

| G | CA_ODT  | MIR  | VDD   | $\times$  | $\times$ | ${\succ}$ | CK_t   | VDDQ | TEN     | G |

| н | ALERT_n | GND  | CS_n  | $\bowtie$ | $\times$ | $\succ$   | CK_c   | GND  | VDD     | Н |

| J | VDDQ    | CA4  | CA0   | $\bowtie$ | $\times$ | ${\succ}$ | CA1    | CA5  | VDDQ    | J |

| к | VDD     | CA6  | CA2   | $\bowtie$ | $\times$ | $\succ$   | CA3    | CA7  | VDD     | к |

| L | VDDQ    | GND  | CA8   | $\bowtie$ | Х        | ${\succ}$ | CA9    | GND  | VDDQ    | L |

| м | CAI     | CA10 | CA12  | $\bowtie$ | $\succ$  | $\succ$   | CA13   | CA11 | RESET_n | м |

| N | VDD     | GND  | VDD   | $\succ$   | $\succ$  | $\succ$   | VPP    | GND  | VDD     | N |

|   | 1       | 2    | 3     | 4         | 5        | 6         | 7      | 8    | 9       | - |

# DDR5 78-ball Footprint Signal Mapping Into the W5643A

# Connecting the W5643A to a U4164A logic analyzer with U4208A and U4209A probe/cables:

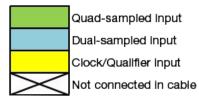

### Signals and logic analyzer channel mapping to the W5643A

| Logic Analyzer Pod<br>and its Channels |      | Signals Logic Analyzer Po<br>from and its Channels<br>U4208A<br>Pod A |                            |      | Signals<br>from<br>U4209A<br>Pod A | Logic Analyzer Pod<br>and its Channels |      | Signals<br>from<br>U4209A<br>Pod B                                          | Logic Analyzer Pod<br>and its Channels |      | Signals<br>from<br>U4208<br>A Pod B |

|----------------------------------------|------|-----------------------------------------------------------------------|----------------------------|------|------------------------------------|----------------------------------------|------|-----------------------------------------------------------------------------|----------------------------------------|------|-------------------------------------|

|                                        | 0    |                                                                       |                            | 0    |                                    |                                        | 0    |                                                                             |                                        | 0    | DQ5                                 |

|                                        | 1    |                                                                       |                            | 1    |                                    |                                        | 1    | $\left \right>$                                                             |                                        | 1    | $\left \times\right $               |

|                                        | 2    |                                                                       |                            | 2    | CA2                                |                                        | 2    | DQ4                                                                         |                                        | 2    | DQ7                                 |

|                                        | 3    | CA3                                                                   | Pod 3<br>(Dual<br>sampled) | 3    | CA12                               | <b>Pod 5</b><br>(Quad<br>sampled)      | 3    | $\geq$                                                                      |                                        | 3    | $\left \times\right $               |

|                                        | 4    | CA13                                                                  |                            | 4    | CA8                                |                                        | 4    | DQ6                                                                         |                                        | 4    | DQ1                                 |

|                                        | 5    | CA9                                                                   |                            | 5    |                                    |                                        | 5    | $\left \right>$                                                             |                                        | 5    | $\left \times\right $               |

|                                        | 6    | RESET_n                                                               |                            | 6    | CA10                               |                                        | 6    | DQS_c                                                                       |                                        | 6    | DM_n                                |

| Pod 1                                  | 7    | CA11                                                                  |                            | 7    | CAI                                |                                        | 7    | $>\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | Pod 7                                  | 7    | $\left \times\right $               |

| (Dual<br>sampled)                      | 8    | CA7                                                                   |                            | 8    |                                    |                                        | 8    | DQ0                                                                         | (Quad<br>sampled                       | 8    | LBDQS                               |

|                                        | 9    | CA5                                                                   |                            | 9    |                                    |                                        | 9    | $\left \times\right $                                                       | )                                      | 9    | $\left \times\right $               |

|                                        | 10   |                                                                       |                            | 10   | CA6                                |                                        | 10   | LBDQ                                                                        |                                        | 10   | DQ3                                 |

|                                        | 11   | CA1                                                                   |                            | 11   | CA4                                |                                        | 11   | $\left \right>$                                                             |                                        | 11   | $\left \times\right $               |

|                                        | 12   |                                                                       |                            | 12   | CA0                                |                                        | 12   | DQ2                                                                         |                                        | 12   |                                     |

|                                        | 13   |                                                                       |                            | 13   | ALERT_n                            |                                        | 13   | $\left \right>$                                                             |                                        | 13   | $\left \times\right $               |

|                                        | 14   |                                                                       |                            | 14   | CS_n                               |                                        | 14   | DQS_t                                                                       |                                        | 14   | MIR                                 |

|                                        | 15   |                                                                       |                            | 15   | CA_ODT                             |                                        | 15   | $\left \right>$                                                             |                                        | 15   | $\left \times\right $               |

|                                        | CLK  | CK_c                                                                  |                            | CLK  |                                    |                                        | CLK  |                                                                             |                                        | CLK  |                                     |

|                                        | CLK# | CK_t                                                                  |                            | CLK# |                                    |                                        | CLK# |                                                                             |                                        | CLK# |                                     |

### W5643A is available in three different quantity options:

- W5643A-001 Qty (1), DDR5 BGA Interposer, 78-ball, 2-wing, connects to U4208A/U4209A

- W5643A-002 Qty (2), DDR5 BGA Interposer, 78-ball, 2-wing, connects to U4208A/U4209A

- W5643A-004 Qty (4), DDR5 BGA Interposer, 78-ball, 2-wing, connects to U4208A/U4209A

### Typical configuration

#### Hardware:

- Qty (1) U4164A logic analyzer module (required)

- Qty (1) U4164A-02G increase maximum speeds to 4GT/s (Required)

- Qty (1) U4164A-008 increase maximum memory depth to 8Mb (Optional, user selects memory depth option)

- Qty (1) M9502A AXIe 2-slot chassis with ESM USB option (Can be substituted with M9505A 5-slot chassis)

- Qty (1) M9537A AXIe High Performance Embedded Controller, with keyboard, mouse and windows 10 options (Can substitute with Y1202A PCIe Cable, M9048A PCIe Desktop Adapter, and user supplied host Desktop.)

#### Software:

- Qty (1) B4661A Memory analysis SW (Required)

- Qty (1) licensed option: B4661A-5FP (Highly Recommended)

#### Probing Required:

- Qty (1) W4643A-001 quantity 1 DDR4 x4/x8 BGA interposer, 78-ball, 2-wing

- Qty (1) U4208A probe/cable, 61-pin ZIF, no RC, 160-pin direct connect to LA

- Qty (1) U4209A probe/cable, 61-pin ZIF, no RC, 160-pin direct connect to LA

Please refer to the Keysight W5643A DDR5 and W4640A/30A Series DDR4 BGA Interposers Installation Guide for details on installation.

## Learn more at: www.keysight.com

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus